# DLC75B ( .110" x .110")

## **♦ DLC75B Capacitance & Rated Voltage Table**

Remark: special capacitance, tolerance and WVDC are available, consult with DALICAP.

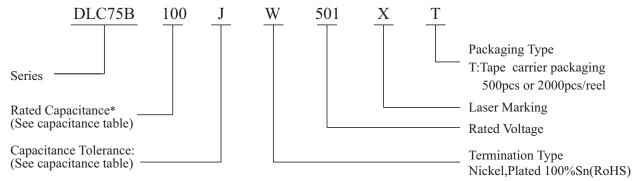

#### ◆ Part Numbering

<sup>\*</sup> When capacitance is less than 1.0, use "R" for decimal

| Code      | A            | В      | С             | D       | F   | G   | J    |

|-----------|--------------|--------|---------------|---------|-----|-----|------|

| Tolerance | $\pm0.05 pF$ | ±0.1pF | $\pm 0.25 pF$ | ± 0.5pF | ±1% | ±2% | ± 5% |

#### **◆DLC75B Chip Dimensions**

unit:inch(millimeter)

|        | Term.<br>Code | Type / Outlines | Capacitor Dimensions                         |                                  |                       |                                  | Dioted             |

|--------|---------------|-----------------|----------------------------------------------|----------------------------------|-----------------------|----------------------------------|--------------------|

| Series |               |                 | Length (Lc)                                  | Width (Wc)                       | Thickness (Tc)        | Overlap<br>(B)                   | Plated<br>Material |

| DLC75B | W             | Tel             | .110<br>+.020~010<br>(2.79+<br>+0.51~ -0.25) | .110<br>±.010<br>(2.79<br>±0.25) | .102<br>(2.60)<br>max | .016<br>~.039<br>(0.40~<br>1.00) | Sn/Ni<br>(RoHS)    |

#### ◆ Design Kits

These capacitors are 100% RoHS. Kits contain 10(ten) pieces per value; number of values per kit varies, depending on case size and capacitance.

| Kit        | Description (pF) | Values (pF)                                                                              | Tolerance             |

|------------|------------------|------------------------------------------------------------------------------------------|-----------------------|

| DKDLC75B01 | 0.2 - 10         | 0.2, 0.5, 0.7, 0.8, 1.0, 1.2, 1.5, 1.8, 2.0, 2.4, 2.7, 3.0, 3.3, 3.9, 4.7, 5.6, 6.8, 8.2 | $\pm0.10 \mathrm{pF}$ |

| DKDLC75B02 | 10 - 100         | 10                                                                                       | ± 5%                  |

|            |                  | 10, 12, 15, 18, 20, 22, 24, 27, 30, 33, 39, 47, 56, 68, 82, 100                          | ±5%                   |

| DKDLC75B03 | 100 - 1000       | 100, 120, 150, 180, 200, 220, 240, 270, 300, 390, 470, 560, 680, 820, 1000               | ±5%                   |

#### **♦** Performance

| Item                                  | Specifications                                                                                                                                                                       |  |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Quality Factor (Q)                    | 2,000 min.                                                                                                                                                                           |  |  |

| Insulation Resistance (IR)            | 10 <sup>5</sup> Megohms min. @ +25℃ at rated WVDC.                                                                                                                                   |  |  |

| Rated Voltage                         | See capacitance table                                                                                                                                                                |  |  |

| Dielectric Withstanding Voltage (DWV) | 250% of Voltage for 5 seconds, Rated Voltage \le 500VDC  150% of Voltage for 5 seconds, 500VDC < Rated Voltage \le 1250VDC  120% of Voltage for 5 seconds, Rated Voltage \le 1250VDC |  |  |

| Operating Temperature Range           | -55℃ to +125℃                                                                                                                                                                        |  |  |

| Temperature Coefficient (TC)          | 0 ± 30ppm/℃                                                                                                                                                                          |  |  |

| Capacitance Drift                     | $\pm$ 0.2% or $\pm$ 0.05pF, whichever is greater.                                                                                                                                    |  |  |

| Piezoelectric Effects                 | None                                                                                                                                                                                 |  |  |

## **♦**Environmental Tests

| Item                         | Specifications                                                                                                                | Method                                                                                                                                                                                                                                    |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Terminal<br>Adhesion         | Termination should not pull off.<br>Ceramic should remain undamaged.                                                          | Linear pull force exerted on axial leads soldered to each terminal. 2.0lbs.                                                                                                                                                               |

| Resistance to soldering heat | No mechanical damage<br>Capacitance change: $-1.0\% \sim +2.0\%$<br>Q>500<br>I.R. >10 G Ohms<br>Breakdown voltage: 2.5 x WVDC | Preheat device to 150°C-180°C for 60 sec.  Dip in 260°±5°C solder for 10±1 sec.  Measure after 24±2 hours cooling period.                                                                                                                 |

| Thermal<br>Shock             | No mechanical damage<br>Capacitance change:±0.5% or 0.5pF max<br>Q>2000<br>I.R. >10 G Ohms<br>Breakdown voltage: 2.5 x WVDC   | MIL-STD-202, Method 107, Condition A. At the maximum rated temperature stay 30 minutes. The time of removing shall not be more than 3 minutes. Perform the five cycles.                                                                   |

| Humidity,<br>Steady State    | No mechanical damage<br>Capacitance change: ±0.5% or 0.5pF max.<br>Q>300<br>I.R. >1 G Ohms<br>Breakdown voltage: 2.5 x WVDC   | MIL-STD-202, Method 106.                                                                                                                                                                                                                  |

| Low Voltage<br>Humidity      | No mechanical damage<br>Capacitance change: ±0.3% or 0.3pF max.<br>Q>300<br>I.R. >1 G Ohms<br>Breakdown voltage: 2.5 x WVDC   | MIL-STD-202, Method 103, Condition A, with 1.5 Volts D.C. applied while subjected to an environment of 85°C with 85% relative humidity for 240 hours minimum.                                                                             |

| Life                         | No mechanical damage<br>Capacitance change: ±2.0% or 0.5pF max.<br>Q>500<br>I.R. >1 G Ohms<br>Breakdown voltage: 2.5 x WVDC   | MIL-STD-202, Method 108, for 1000 hours, at 125°C.  200% of Voltage for Capacitors, Rated Voltage \le 500VDC  120% of Voltage for Capacitors, 500VDC < Rated Voltage \le 1250VDC  100% of Voltage for Capacitors, Rated Voltage > 1250VDC |

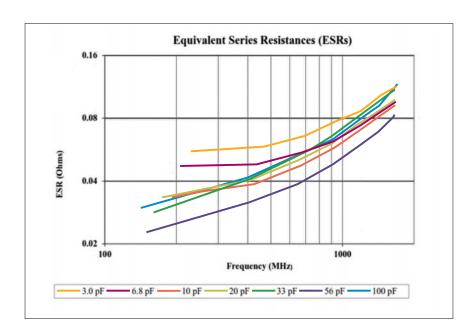

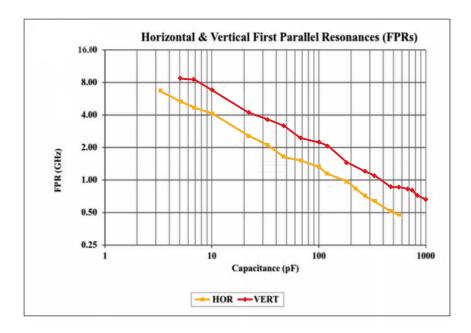

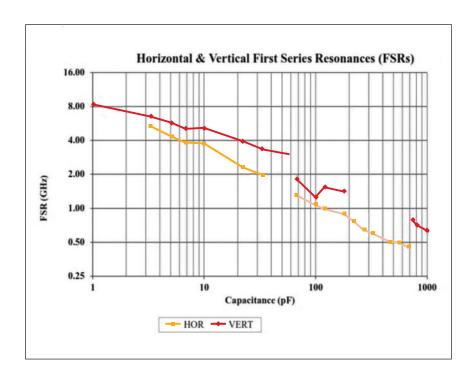

### **♦ DLC75B Performance Curve**

The First Parallel Resonance, FPR, is defined as the lowest frequency at which a suckout or notch appears in |S21|. It is generally independent of substrate thickness or dielectric constant, but does depend on capacitor orientation. A horizontal orientation means the capacitor electrode planes are parallel to the plane of the substrate; a vertical orientation means the electrode planes are perpendicular to the substrate.

The First Series Resonance, FSR, is defined as the lowest frequency at which the imaginary part of the input impedance,  $\operatorname{Im}[\operatorname{Zin}]$ , equals zero. Should  $\operatorname{Im}[\operatorname{Zin}]$  or the real part of the input impedance,  $\operatorname{Re}[\operatorname{Zin}]$ , not be monotonic with frequency at frequencies lower than those at which  $\operatorname{Im}[\operatorname{Zin}] = 0$ , the FSR shall be considered as undefined. FSR is dependent on internal capacitor structure; substrate thickness and dielectric constant; capacitor orientation, as defined alongside the FPR plot; and mounting pad dimensions.

#### **Definitions and Measurement conditions:**

The definitions on the charts are for a capacitor in a series configuration, i.e., mounted across a gap in a microstrip trace with a 50-Ohm termination. The measurement conditions are: substrate -- Rogers RO4350; substrate dielectric constant = 3.48; horizontal mount substrate thickness (mils) = 55; vertical mount substrate thickness (mils) = 45; gap in microstrip trace, horizontal or vertical mount (mils) = 61.1; horizontal mount microstrip trace width (mils) = 123.7; vertical mount microstrip trace width (mils) = 101.0. **Reference planes at sample edges.** All data has been derived from electrical models created by Modelithics, Inc., a specialty vendor contracted by DLC. The models are derived from measurements on a large number of parts disposed on several different substrates.