## DLC75N(0201)

## **◆DLC75N Capacitance & Rated Voltage Table**

| Cap.pF | Code | Tol.        | Rated<br>WVDC | Cap.pF | Code | Tol.        | Rated<br>WVDC | Cap.pF | Code | Tol.      | Rated<br>WVDC      |  |  |

|--------|------|-------------|---------------|--------|------|-------------|---------------|--------|------|-----------|--------------------|--|--|

|        |      |             |               | 2.2    | 2R2  |             |               | 16     | 160  |           |                    |  |  |

| 0.2    | 0R2  |             |               | 2.4    | 2R4  |             |               | 18     | 180  |           |                    |  |  |

| 0.3    | 0R3  |             |               | 2.7    | 2R7  |             |               |        |      |           |                    |  |  |

| 0.4    | 0R4  |             |               | 3.0    | 3R0  | A,B,<br>C,D |               |        |      |           |                    |  |  |

| 0.5    | 0R5  |             |               | 3.3    | 3R3  |             |               |        |      |           |                    |  |  |

| 0.6    | 0R6  |             |               | 3.6    | 3R6  |             |               |        |      |           |                    |  |  |

| 0.7    | 0R7  |             |               | 3.9    | 3R9  |             |               |        |      | F,G,<br>J | 25V<br>Code<br>250 |  |  |

| 0.8    | 0R8  | A,B,<br>C,D | 25V           | 4.3    | 4R3  |             |               |        |      |           |                    |  |  |

| 0.9    | 0R9  |             | Code          | 4.7    | 4R7  |             |               |        |      |           |                    |  |  |

| 1.0    | 1R0  |             |               | 5.1    | 5R1  |             |               |        |      |           |                    |  |  |

| 1.1    | 1R1  |             |               | 5.6    | 5R6  |             |               |        |      |           |                    |  |  |

| 1.2    | 1R2  |             |               | 6.2    | 6R2  | B,C<br>F,G, |               |        |      |           |                    |  |  |

| 1.3    | 1R3  |             |               | 6.8    | 6R8  |             |               |        |      |           |                    |  |  |

| 1.4    | 1R4  |             |               | 7.5    | 7R5  |             | B,C           | B,C    |      |           |                    |  |  |

| 1.5    | 1R5  |             |               | 8.2    | 8R2  |             |               |        |      |           |                    |  |  |

| 1.6    | 1R6  |             |               | 9.1    | 9R1  |             |               |        |      |           |                    |  |  |

| 1.7    | 1R7  |             |               | 10     | 100  |             |               |        |      |           |                    |  |  |

| 1.8    | 1R8  |             |               | 11     | 110  |             |               |        |      |           |                    |  |  |

| 1.9    | 1R9  |             |               | 12     | 120  |             |               |        |      |           |                    |  |  |

| 2.0    | 2R0  |             |               | 13     | 130  |             | J             |        |      |           |                    |  |  |

| 2.1    | 2R1  |             |               | 15     | 150  |             |               |        |      |           |                    |  |  |

Remark: special capacitance, tolerance and WVDC are available, consult with DALICAP.

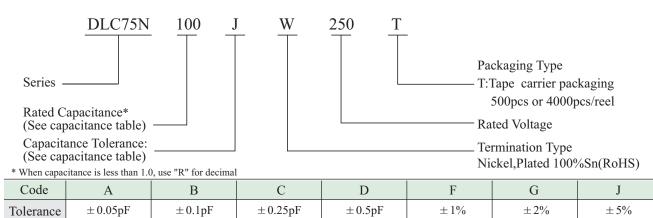

### **♦ Part Numbering**

## **♦ DLC75N Chip Dimensions**

unit:inch(millimeter)

|        | Term.<br>Code |                 |                                   | Dlatad                            |                                      |                                  |                    |

|--------|---------------|-----------------|-----------------------------------|-----------------------------------|--------------------------------------|----------------------------------|--------------------|

| Series |               | Type / Outlines | Length (Lc)                       | Width<br>(Wc)                     | Thickness (Tc)                       | Overlap<br>(B)                   | Plated<br>Material |

| DLC75N | W             | Tel             | $.024 \pm .001$ $(0.60 \pm 0.03)$ | $.012 \pm .001$ $(0.30 \pm 0.03)$ | $.012 \pm .001$<br>$(0.30 \pm 0.03)$ | .004<br>~.008<br>(0.10~<br>0.20) | Sn/Ni<br>(RoHS)    |

### ◆ Design Kits

These capacitors are 100% RoHS. Kits contain 10(ten) pieces per value; number of values per kit varies, depending on case size and capacitance.

| Kit        | Description (pF) | Values (pF)                                                               | Tolerance |

|------------|------------------|---------------------------------------------------------------------------|-----------|

| DKDLC75N01 | 0.2 - 2.0        | 0.2, 0.3, 0.5, 0.7, 0.8, 0.9, 1.0, 1.3, 1.5, 1.7, 1.9, 2.0                | ±0.10pF   |

| DKDLC75N02 | 1.0 - 10         | 1.0, 1.3, 1.5, 1.7, 1.9, 2.0, 2.2, 2.7, 3.0, 3.9, 4.7, 5.6, 6.8, 7.5, 8.2 | ±0.10pF   |

|            | 1.0 - 10         | 10                                                                        | ± 5%      |

| DKDLC75N03 | 10 - 18          | 10, 12, 13, 15, 16, 18                                                    | ± 5%      |

### **♦** Performance

| Item                                  | Specifications                                       |  |  |

|---------------------------------------|------------------------------------------------------|--|--|

| Quality Factor (Q)                    | 2,000 min.                                           |  |  |

| Insulation Resistance (IR)            | 10 <sup>5</sup> Megohms min. @ +25 °C at rated WVDC. |  |  |

| Rated Voltage                         | 25V                                                  |  |  |

| Dielectric Withstanding Voltage (DWV) | 250% of rated voltage for 5 seconds.                 |  |  |

| Operating Temperature Range           | -55°C to +150°C                                      |  |  |

| Temperature Coefficient (TC)          | 0 ± 30ppm/℃                                          |  |  |

| Capacitance Drift                     | $\pm 0.2\%$ or $\pm 0.05$ pF, whichever is greater.  |  |  |

| Piezoelectric Effects                 | None                                                 |  |  |

# **♦** Environmental Tests

| Item                      | Specifications                           | Method                                                                                                      |  |  |

|---------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|

| Terminal                  | Termination should not pull off.         | Linear pull force exerted on axial leads soldered to                                                        |  |  |

| Adhesion                  | Ceramic should remain undamaged.         | each terminal. 2.0lbs.                                                                                      |  |  |

|                           | No mechanical damage                     |                                                                                                             |  |  |

| Resistance                | Capacitance change: $-1.0\% \sim +2.0\%$ | Preheat device to 150°C-180°C for 60 sec.                                                                   |  |  |

| to soldering heat         | Q>500                                    | Dip in 260°±5°C solder for 10±1 sec.                                                                        |  |  |

|                           | I.R. >10 G Ohms                          | Measure after 24±2 hours cooling period.                                                                    |  |  |

|                           | Breakdown voltage: 2.5 x WVDC            |                                                                                                             |  |  |

|                           | No mechanical damage                     | MIL-STD-202, Method 107, Condition A.                                                                       |  |  |

|                           | Capacitance change:±0.5% or 0.5pF max    | At the maximum rated temperature stay 30 minutes.                                                           |  |  |

| Thermal                   | Q>2000                                   | The time of removing shall not be more than 3 minutes.                                                      |  |  |

| Shock                     | I.R. >10 G Ohms                          | Perform the five cycles.                                                                                    |  |  |

|                           | Breakdown voltage: 2.5 x WVDC            |                                                                                                             |  |  |

|                           | No mechanical damage                     |                                                                                                             |  |  |

|                           | Capacitance change: ±0.5% or 0.5pF max.  | MIL-STD-202, Method 106.                                                                                    |  |  |

| Humidity,<br>Steady State | Q>300                                    |                                                                                                             |  |  |

| Steady State              | I.R. >1 G Ohms                           |                                                                                                             |  |  |

|                           | Breakdown voltage: 2.5 x WVDC            |                                                                                                             |  |  |

|                           | No mechanical damage                     |                                                                                                             |  |  |

| T 37-14                   | Capacitance change: ±0.3% or 0.3pF max.  | MIL-STD-202, Method 103, Condition A, with 1.5 Volts                                                        |  |  |

| Low Voltage<br>Humidity   | Q>300                                    | D.C. applied while subjected to an environment of 85                                                        |  |  |

| ,                         | I.R. >1 G Ohms                           | with 85% relative humidity for 240 hours minimum.                                                           |  |  |

|                           | Breakdown voltage: 2.5 x WVDC            | -                                                                                                           |  |  |

|                           | No mechanical damage                     |                                                                                                             |  |  |

|                           | Capacitance change: ±2.0% or 0.5pF max.  | MIL-STD-202, Method 108, for 2000 hours, at the maximum rated temperature, 200% Rated voltage D.C. applied. |  |  |

| Life                      | Q>500                                    |                                                                                                             |  |  |

|                           | I.R. >1 G Ohms                           |                                                                                                             |  |  |

|                           | Breakdown voltage: 2.5 x WVDC            | rr                                                                                                          |  |  |

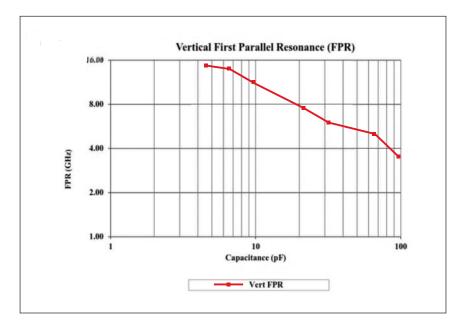

#### **◆ DLC75N Performance Curve**

The First Parallel Resonance, FPR, is defined as the lowest frequency at which a suckout or notch appears in |S21|. It is generally independent of substrate thickness or dielectric constant, but does depend on capacitor orientation. A horizontal orientation means the electrode planes are parallel to the substrate.

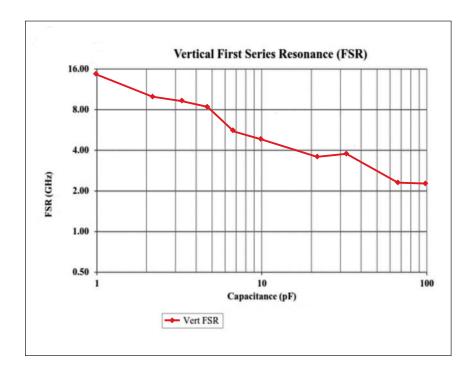

### **◆ DLC75N Performance Curve**

The First Series Resonance, FSR, is defined as the lowest frequency at which the imaginary part of the input impedance, Im[Zin], equals zero. Should Im[Zin] or the real part of the input impedance, Im[Zin], not be monotonic with frequency at frequencies lower than those at which Im[Zin] = 0, the FSR shall be considered as undefined. FSR is dependent on internal capacitor structure; substrate thickness and dielectric constant; capacitor orientation, as defined alongside the FPR plot; and mounting pad dimensions.

#### **Definitions and Measurement Conditions:**

The definitions on the FPR and FSR charts are for a capacitor in a series configuration, i.e., mounted across a gap in a microstrip trace with a 50-Ohm termination. The measurement conditions are: substrate -- Rogers RO3006; substrate dielectric constant = 6.15; substrate thickness (mils) = 10; gap in microstrip trace (mils) = 6.0; microstrip trace width (mils) = 14.1; Reference planes at sample edges.

All data has been derived from electrical models created by Modelithics, Inc., a specialty vendor contracted by DALICAP. The models are derived from measurements on a large number of parts disposed on several different substrates.